触发器

10.2 基本触发器

一、触发器的概念

复习:组合电路的定义?构成其电路的门电路有何特点?组合电路与时序电路的区别?

门电路:在某一时刻的输出信号完全取决于该时刻的输入信号,没有记忆作用。

触发器:具有记忆功能的基本逻辑电路,能存储二进制信息(数字信息)。

触发器有三个基本特性:

(1)有两个稳态,可分别表示二进制数码0和1,无外触发时可维持稳态;

(2)外触发下,两个稳态可相互转换(称翻转),已转换的稳定状态可长期保持下来,这就使得触发器能够记忆二进制信息,常用作二进制存储单元。

(3)有两个互补输出端,分别用Q和![]() 表示。

表示。

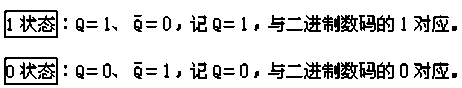

二、触发器的两个稳定状态

通常用Q端的输出状态来表示触发器的状态

三、触发器的分类:

根据逻辑功能不同:RS触发器、D触发器、JK触发器、T触发器和 触发器等。

触发方式不同:电平触发器、边沿触发器和主从触发器等。

电路结构不同:基本RS触发器,同步触发器、维持阻塞触发器、主从触发器和边沿触发器等。

基本RS触发器

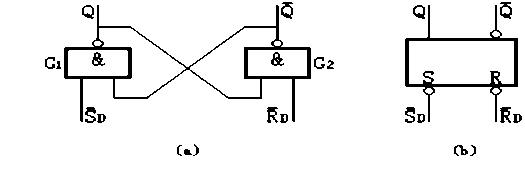

(一)由与非门组成的基本RS触发器

1.电路结构

电路组成:两个与非门输入和输出交叉耦合(反馈延时)。如图所示。

逻辑符号:图(b)所示。

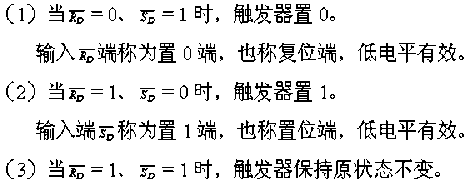

2.逻辑功能

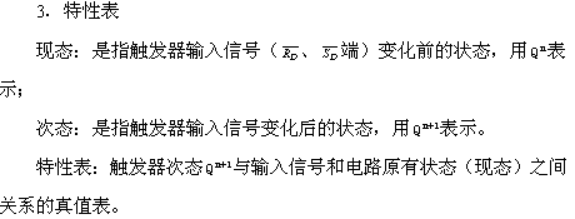

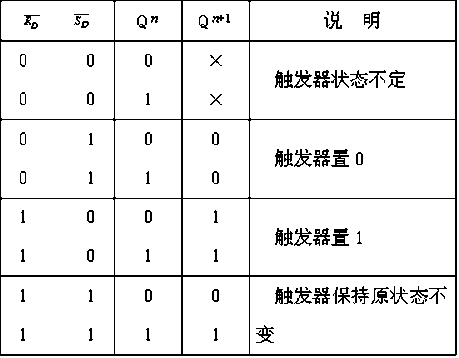

与非门组成的基本RS触发器的特性表

4. 基本RS触发器的触发方式:

端的输入信号直接控制。(电平直接触发)在实际工作中,要求触发器按一定的节拍翻转。

措施:加入时钟控制端CP,触发器的状态翻转按CP节拍。

同步触发器(时钟触发器或钟控触发器):具有时钟脉冲CP控制的触发器。

CP:控制时序电路工作节奏的固定频率的脉冲信号,一般是矩形波。

同步:因为触发器状态的改变与时钟脉冲同步。

同步触发器的翻转时刻:受CP控制

触发器翻转到何种状态:由输入信号决定

(二)其他触发器及触发器的触发方式

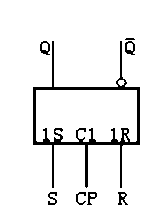

(1)同步RS触发器

1.电路结构

逻辑符号:如图所示。

钟控端(CP端):时钟脉冲输入端。

2.逻辑功能

工作原理。(边分析边列特性表。)

当CP=0时,G3、G4被封锁,都输出1,触发器的状态保持不变,

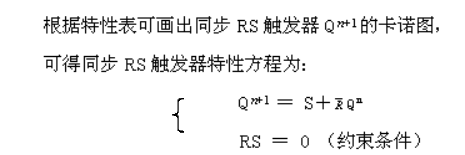

1. 特性方程

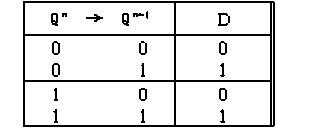

(2)同步D触发器

1.电路结构

为了避免同步RS触发器出现R=S=1的情况,可在R和S之间接入非门G5

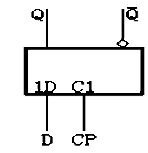

逻辑符号:如图所示。

2.逻辑功能

回忆:同步RS触发器的逻辑功能?

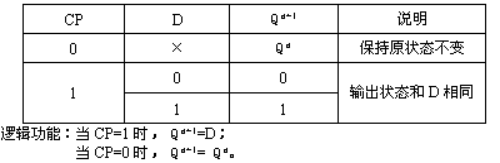

将同步RS触发器特性表的中的S=D,R= ,就简化为D触发器的特性表

,就简化为D触发器的特性表

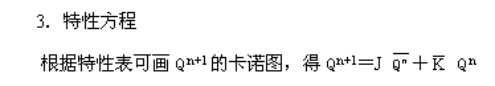

根据特性表可得到在CP=1时的同步D触发器的驱动表。

3.特性方程

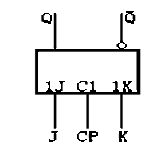

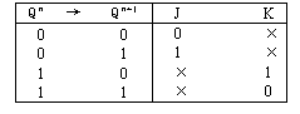

(3)同步JK触发器

1.电路结构

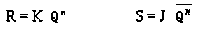

克服同步RS触发器在R=S=1时出现不定状态的另一种方法:将触发器输出端Q和 状态反馈到输入端,这样,输出不会同时出现0,从而避免了不定状态的出现。J、K端相当于同步RS触发器的S、R端。

逻辑符号:如图所示。

2.逻辑功能

当CP=0时,G3和G4被封锁,保持。

当CP=1时,G3、G4解除封锁,输入J、K端的信号可控制触发器的状态。

同步JK触发器的驱动表

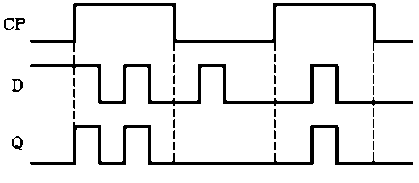

四、同步触发器的空翻

触发器的空翻:在CP为高电平1期间,如同步触发器的输入信号发生多次变化时,其输出状态也会相应发生多次变化的现象。

产生空翻的原因:电平触发方式,在CP高电平期间有效触发

同步触发器由于存在空翻,不能保证触发器状态的改变与时钟脉冲同步,它只能用于数据锁存,而不能用于计数器、移位寄存器和存储器等。

小结

本节主要介绍了基本RS触发器和几种同步触发器,要求掌握几种触发器的逻辑功能和逻辑符号。

触发器的空翻:在CP为高电平1期间,如同步触发器的输入信号发生多次变化时,其输出状态也会相应发生多次变化的现象。

产生空翻的原因:电平触发方式,在CP高电平期间有效触发

同步触发器由于存在空翻,不能保证触发器状态的改变与时钟脉冲同步,它只能用于数据锁存,而不能用于计数器、移位寄存器和存储器等。