时序逻辑电路

10.1 时序逻辑电路

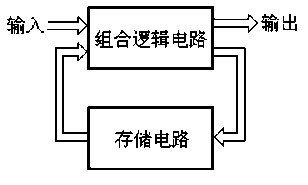

一、定义:

时序逻辑电路(又称时序电路):在任何一个时刻的输出状态不仅取决于当时的输入信号,而且还取决于电路原来的状态。

二、电路构成:

存储电路(主要是触发器,且必不可少) 组合逻辑电路(可选)。

时序逻辑电路的状态是由存储电路来记忆和表示的。

三、分类

根据电路状态转换情况的不同分为:

1.同步时序逻辑电路:

所有触发器的时钟输入端CP都连在一起,在同一个时钟脉冲 CP作用下,凡具备翻转条件的触发器在同一时刻状态翻转。触发器状态的更新和时钟脉冲CP是同步的。

2.异步时序逻辑电路

时钟脉冲CP只接部分触发器的时钟输入端,其余触发器则由电路内部信号触发。因此,凡具备翻转条件的触发器状态的翻转有先有后,并不都和时钟脉冲CP同步。

计数器中,时钟脉冲CP又称为计数脉冲。

四、时序逻辑电路的分析方法

时序逻辑电路的分析:根据给定的电路,写出它的方程、列出状态转换真值表、画出状态转换图和时序图,而后分析出它的功能。

1、分清电路

2、列出三个方程

驱动方程、状态方程、输出方程

3、列出状态真值表

4、状态图

5、功能描述

6、检查电路有无自启动能力

举例分析

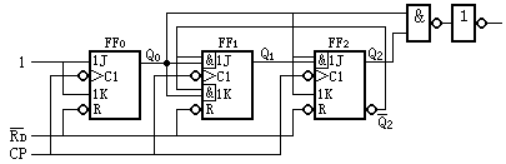

试分析下图所示电路的逻辑功能,并画出状态转换图和时序图。

解:分析步骤

由电路可看出,时钟脉冲CP加在每个触发器的时钟脉冲输入端上。因此它是一个同步时序逻辑电路,时钟方程可以不写。

三个JK触发器的状态更新时刻都对应CP的下降沿。

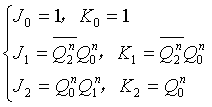

1、写方程式

(1)输出方程

(2)驱动方程

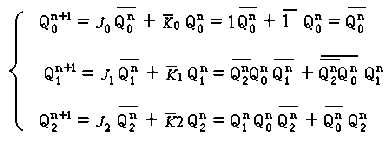

(3)状态方程

将驱动方程带入JK触发器的特性方程,得状态方程

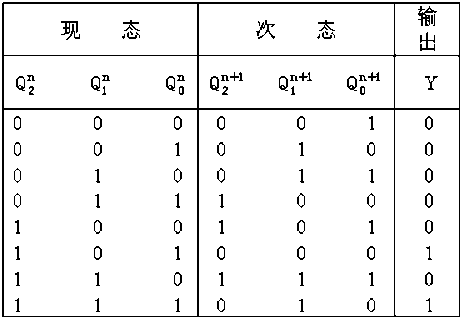

2.状态转换真值表

由状态方程,可列状态转换真值表。

3.逻辑功能说明

由状态转换真值表,在输入第6个计数脉冲CP后,返回原来的状态,同时输出端Y输出一个进位脉冲。因此为同步六进制计数器。

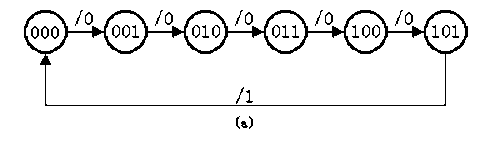

4.画状态转换图和时序图

⑴ 根据状态转换真值表→状态转换图。

圆圈内表示电路的一个状态,箭头表示电路状态的转换方向(现态→次态)

箭头线上方标注的X/Y为转换条件,X为转换前输入变量的取值,Y为输出值

由于本例没有输入变量,故X未标上数值。

⑵ 根据状态转换真值表→时序图(或称工作波形图)。

5.检查电路能否自启动

电路应有8个工作状态,只有6个状态被利用了,称为有效状态。还有110和111没有被利用,称为无效状态。

能够自启动:如果由于某种原因而进入无效状态工作时,只要继续输入计数脉冲CP,电路会自动返回到有效状态工作。

该电路能够自启动。

小结

本节主要介绍了时序逻辑电路的基本知识和分析方法,重点掌握分析时序逻辑电路的方法。