组合逻辑部件

组合逻辑部件是指具有某种逻辑功能的中规模集成组合逻辑电路芯片。

1.加法器

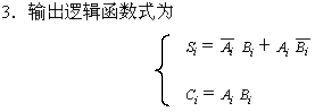

一、半加器

1.只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。

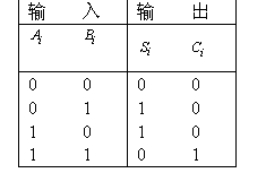

2.真值表

根据二进制加法原则(逢二进一),得出真值表。

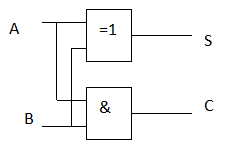

4.逻辑电路:由一个异或门和一个与门组成。

5.逻辑符号

二、全加器

1.不仅考虑两个一位二进制数相加,而且还考虑来自低位进位数相加的运算电路,称为全加器。

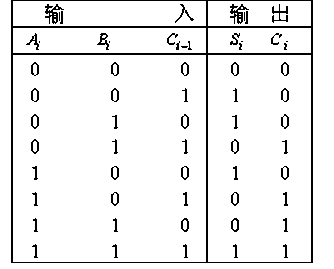

2.真值表

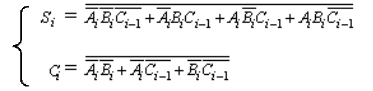

3. 数表达式

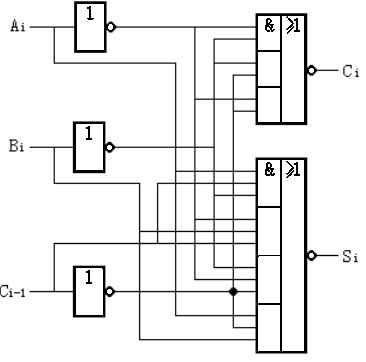

4.逻辑图,所示。

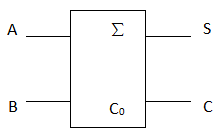

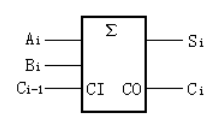

5.逻辑符号

2.编码器

实现编码操作的电路称为编码器。

1、普通编码器:在任何时刻都只能对一个输入信号进行编码,即不允许有两个或两个以上输入信号同时存在的情况出现。

2、优先编码器:允许几个信号同时输入,但是电路只对其中优先级别最高的进行编码。

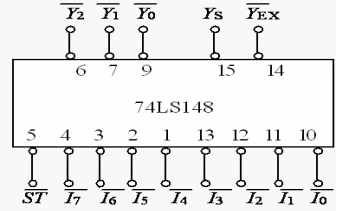

集成8线-3先优先编码器

3、译码器(decoder)

![]()

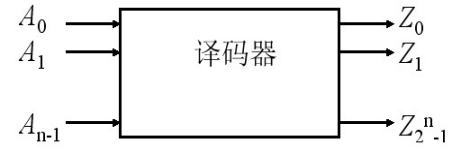

译码器是能够实现译码功能的电路。译码是编码的逆过程,即将某二进制代码翻译成电路的某种状态。一般有n个输入端和m个输出端,满足关系:

![]()

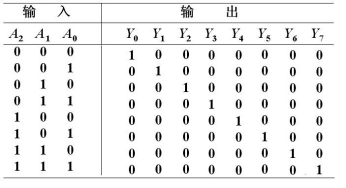

1、二进制译码器(binary-decoder)

将n个输入的组合译成2n种电路状态,也叫n- 2n线译码器。设计3线-8线译码器

(1)列真值表如下

(2)写函数表达式

(3)画逻辑图(略)

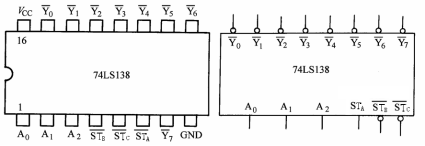

2、集成3线-8线译码器74LS138

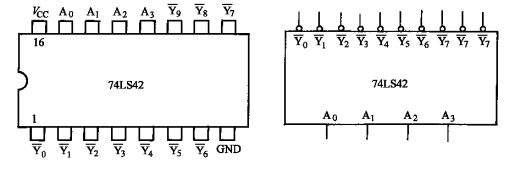

3、二-十进制译码器(Binary-coded decimal decoder)

所谓的二-十进制译码器就是它的输入信号是BCD码,输出是与之相对应的十进制的10个数字。

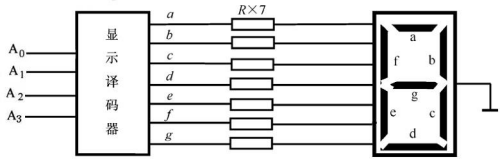

(4)显示译码器

在数字系统中,常需要把处理或测量的结果用人们习惯的十进制数显示出来,这就需要显示译码器。

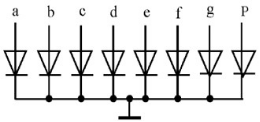

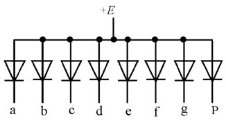

七段字符显示器

共阴极接法 共阳极接法

R为100欧姆左右的限流电阻,防止烧坏显示二级管。

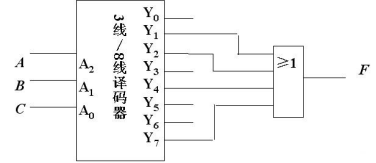

5、用译码器设计组合逻辑电路

例如,试用3线-8线译码器实现逻辑函数:

步骤:

首先将被实现的函数变成以最小项表示的与或表达式,并将被实现函数的变量接到译码器的代码输入端。

当译码器的输出为高电平有效时,选用或门;当输出为低电平有效时,选用与非门。

小结

本节课主要介绍了常见的组合逻辑部件,应掌握各种组合逻辑部件的逻辑符号和逻辑功能,能够利用组合逻辑部件设计电路。